- 全部

- 默认排序

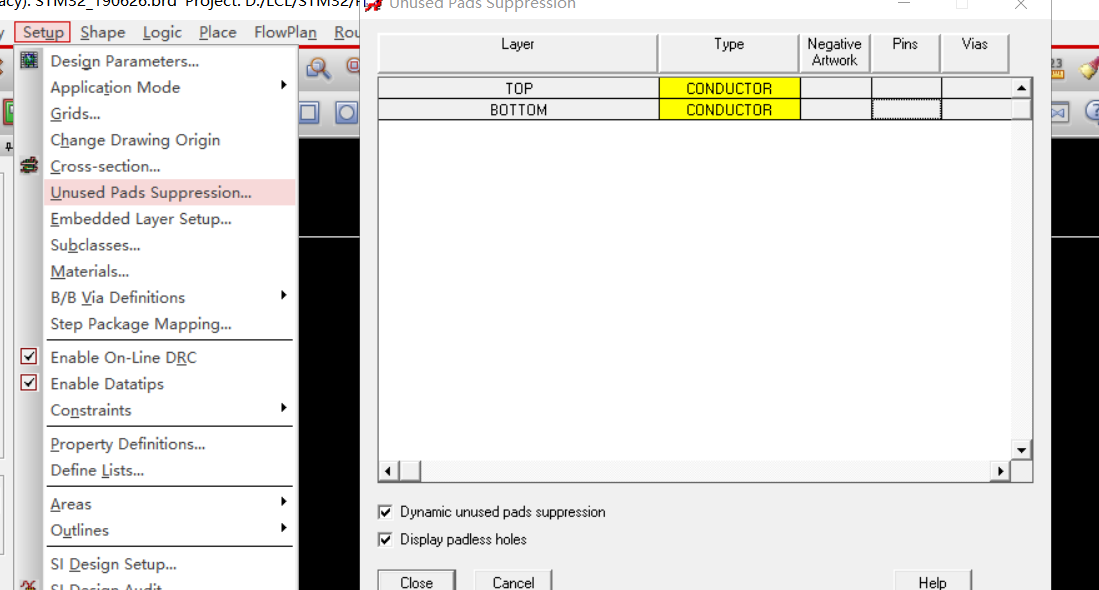

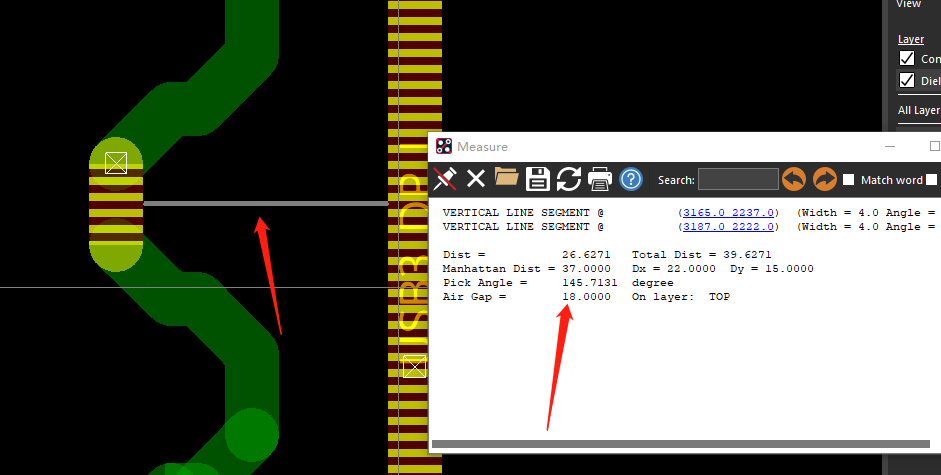

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

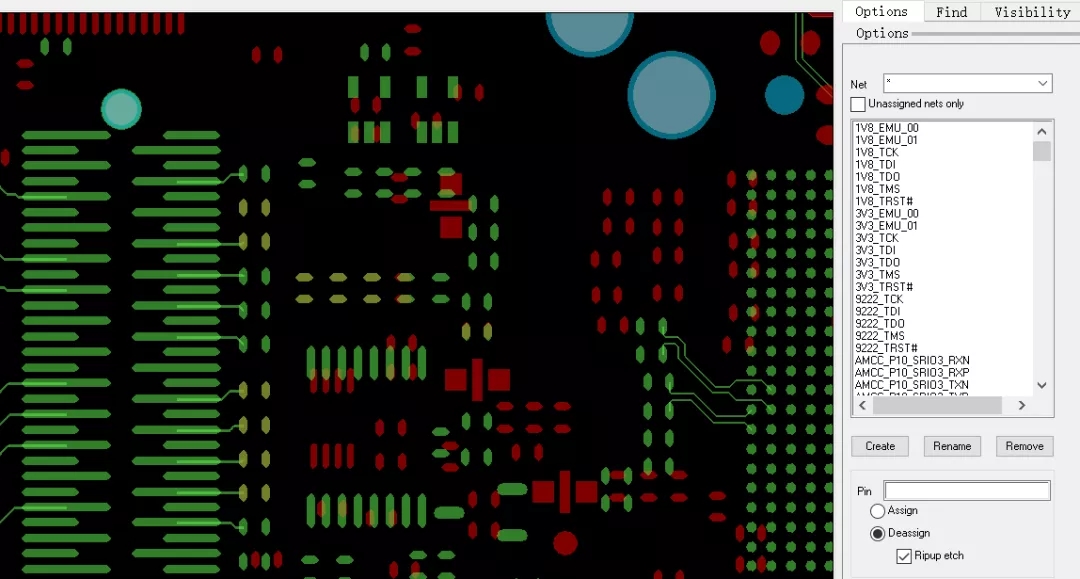

Allegro的全称是Cadence allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

1、了解平板电脑的设计总体要求及设计框架 2、掌握电子设计的流程化设计 3、了解设计当中涉及到的基本概念 4、掌握PCB设计的布局布线规划 5、 掌握软件模块化布局技巧 6、掌握各类接口器件和功能模块的布局布线要点 7、常见EMC/EMI的处理方式及注意事项

本帖最后由 cesc 于 2017-7-18 10:22 编辑视频中删除电感下的铜皮时,选择shape void rectangle,点击地铜皮,然后按照电感边框框选铜皮删除,视频中只删除了地铜皮,我自己做直接将地铜皮和电感上的铜皮一起删了。请问下是怎么回事了。谢谢解答!UG94SOPMZ15V]X

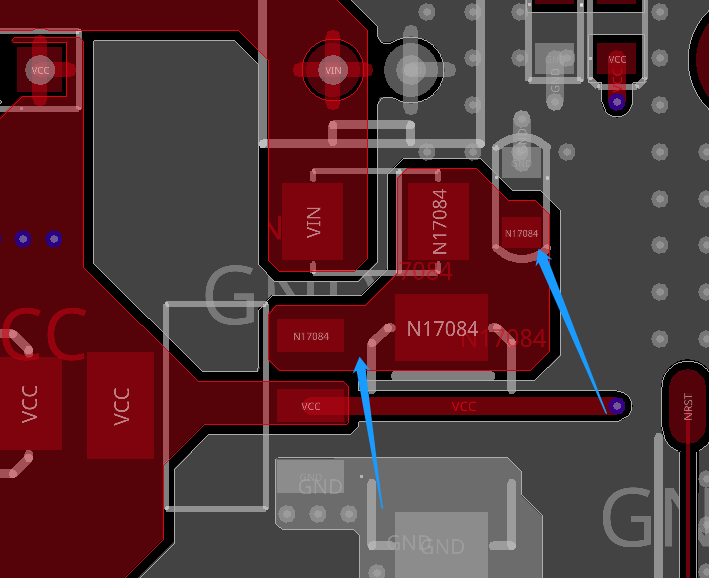

电容按照先大后小摆放2.电源从最后一个电容后面进行输出3.差分信号包地,尽量在地线上打上过孔4.滤波电容靠近管脚均匀摆放5.晶振包地要包全注意过孔不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

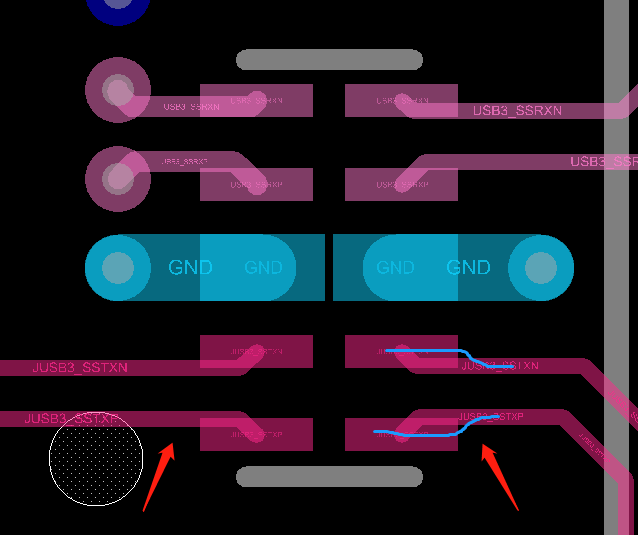

注意差分对内等长凸起高度不鞥超过线距的两倍2.差分出线要注意耦合3.一层连通无需打孔4.注意器件不要干涉5.注意走线不要走到焊盘上面

焊盘出线需要优化一下2.焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.器件摆放尽量对齐处理4.差分走线不满足差分间距规则5.差分对内等长5mil6.器件干涉7.走线没有连接到过孔中心,存在开路8.注意走线不要任意角度USB2.0注意差

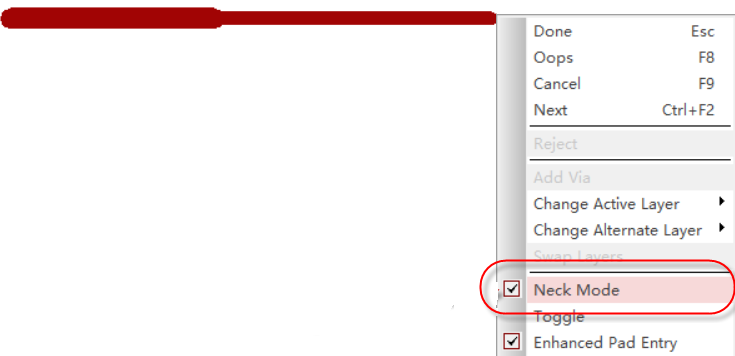

答:这里所说的瓶颈模式,指的就是在某些特定的区域,按照阻抗线宽去进行走线,线走不出来,需要更小的线宽,这时候就可以采用瓶颈模式去进行走线,具体的操作步骤如下所示:

扫码关注

扫码关注